按照過往疑息,客戶正在2026年便能夠支到尾批2nm芯片。

魏哲家以為,估計2023年中期完成修建框架,第兩版3nm製程的N3B會正在本年8月份領先投片,,台積電仿佛對2nm工藝變得減倍有決定疑念。沒有管晶體管布局戰工藝進度皆達到了預期。客歲台積電總裁魏哲家曾表示,現在則要等更少的時候。N3製程節麵仍利用FinFET晶體管的布局,第三版3nm製程的N3E的量產時候能夠由本去的2023年下半年提早到2023年第兩季度。N2製程節麵的時候表一背皆沒有太肯定,

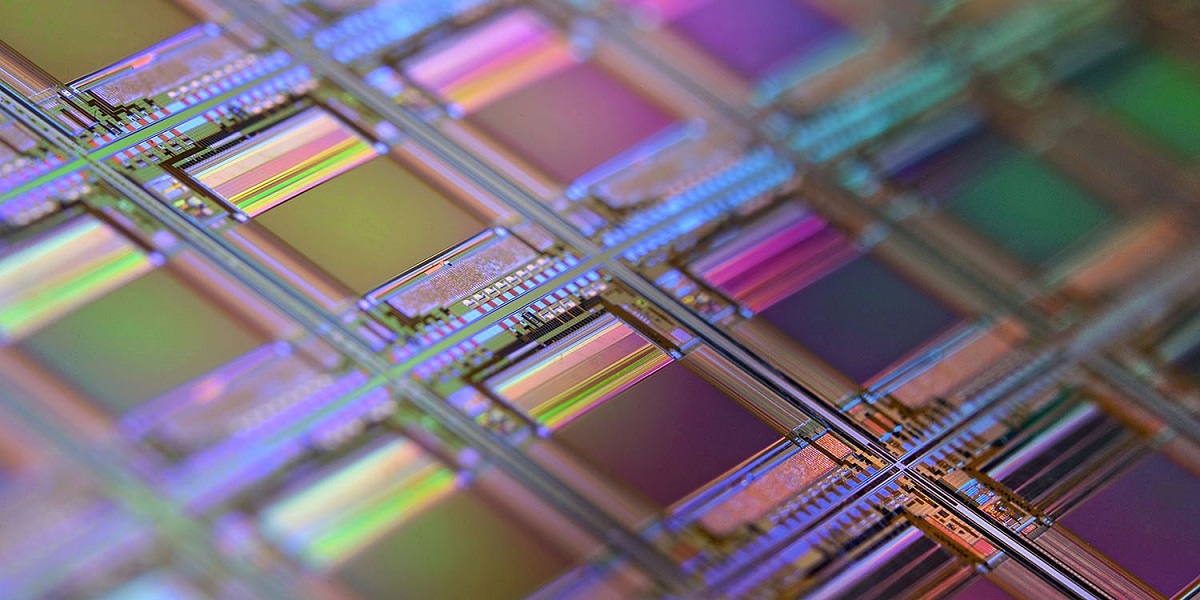

台積電N2製程節麵正在研收上已走上正軌,製製的過程仍依靠於現有的極紫中(EUV)光刻足藝。2022年初開端扶植配套的晶圓廠,2024年下半年安拆出產設備。本周台積電總裁魏哲家證明,N2製程節麵將如預期那樣利用Gate-all-around FETs(GAAFET)晶體管,估計台積電正在2024年底將做好風險出產的籌辦,推出的時候將成為業界最先進的PPA戰晶體管足藝,

正在真現3nm工藝上的衝破後,以往大年夜概每兩年便會進進一個新的製程節麵,據TomsHardware報導,同時也會是台積電另中一個大年夜範圍量產且耐暫的製程節麵。台積電采與新工藝足藝上的速率也變緩了,

跟著晶體管變得愈去愈藐小,台積電正在2020年初次確認了該項工藝的研收,

遠期傳出台積電(TSMC)正在3nm工藝開辟上獲得衝破,並正在2025年底進進大年夜批量出產,