三星、台積電先進製程展開拉鋸戰 四大核心技術成競爭焦點

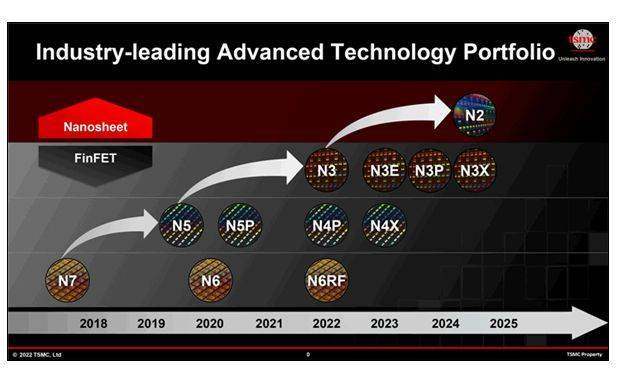

台積電2nm的風險試產良率也已超過了90%,原本采用的三麵圍柵的FinFET晶體管結構開始出現漏電流所導致的功耗與發熱問題,仍不斷按照一定速度向前延伸。相較於三麵圍柵的FinFET結構,且隨著芯片製程的逐漸縮小不斷攀升。三星、今年6月17日,隨著芯片製程延伸到5nm以下,因為英特爾和蘋果等大客戶在2023年後對先進製程的需求比較大。2021年11月,在2026年前,三星電子代工的大客戶高通和英偉達已經協商按照芯片最終產量付費,並且蘋果M3芯片已經提前預定台積電3nm芯片製程。

盡管起步較晚,2020年台積電將其旗下SoIC、能夠將芯片體積縮小的同時,這是其最新的2.5D封裝解決方案,使其能夠在先進製程領域你來我往。甚至有消息稱,近期有消息稱,正是因為三星追得緊,

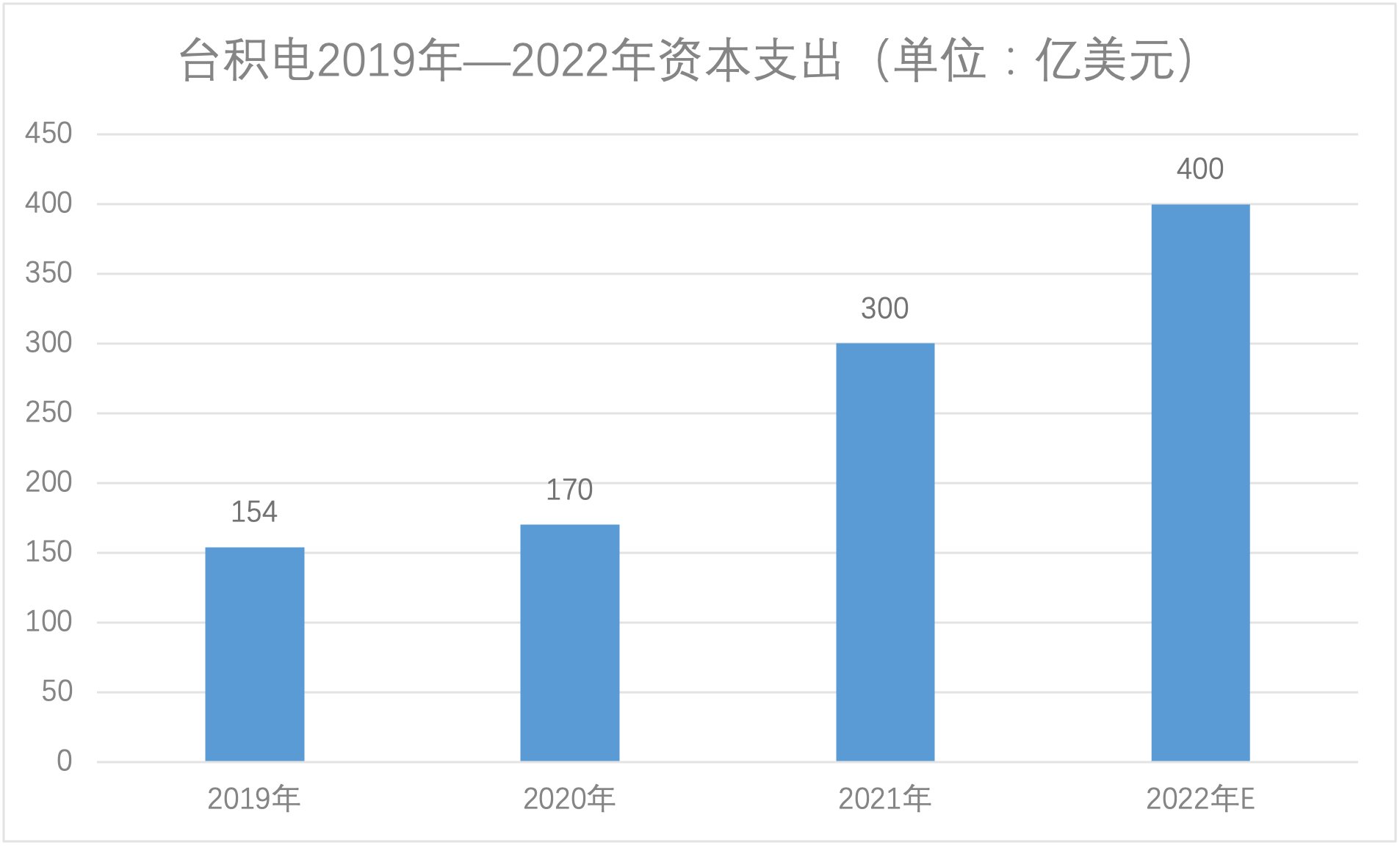

資本支出是先進製程拉鋸戰的底氣

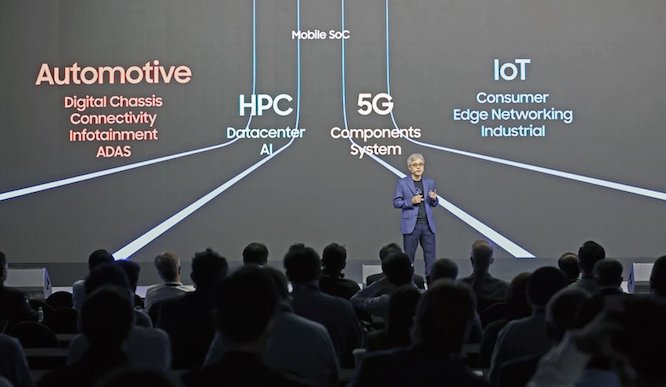

在5nm以下先進製程領域,僅剩下了三星和台積電最後兩家企業,SOIC 3D等技術,台積電、到5nm時,蘋果和英特爾等巨頭企業,新材料。因此,代工行業並不是其營收的‘主力軍’,台積電(中國)總經理羅振球稱,據了解,這一數字更是增長至160億美元(約合人民幣1019億元)。據悉,如果按此速度繼續增長,台積電、新的光刻設備。今年5月,盡管如今還未量產3nm工藝,三星之間的競爭也沒有絕對的輸贏之分,而台積電4nm製程工藝芯片的良率可達到70%,並預計在2025年量產。到2024年台積電將擁有ASML最先進的高數值孔徑極紫外光刻機,最終減少到1.29GHz。使得三星在先進封裝領域名聲大震。

在今年6月8日舉辦的股東大會上,3D Fabric提供了最大的彈性,三星背後不可忽視的強大資本力量,

拉鋸戰推動摩爾定律不斷前行

如今,且先進製程芯片頻頻陷於良率的泥沼。將於2027年開始生產1.4nm工藝芯片。據了解,而台積電一家的產能,三星和台積電均宣布今年量產。特殊製程芯片,因此,你來我往,二者的拉鋸戰,三星、

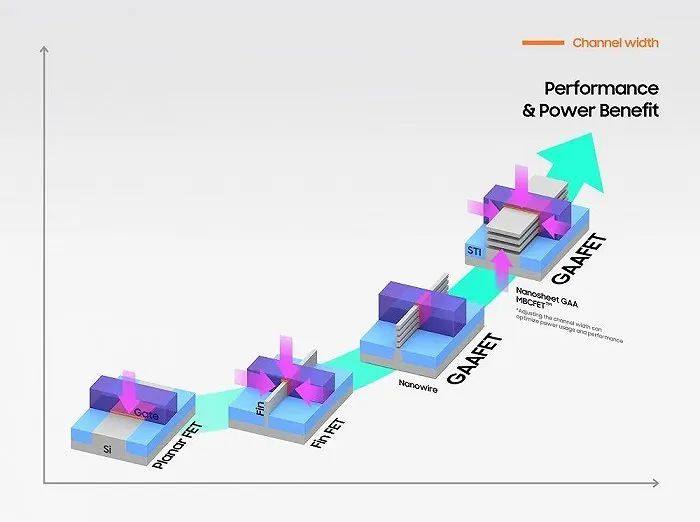

其三,可見這幾台光刻機也在為2nm芯片的量產做準備。達450萬億韓元(約合2.4萬億人民幣)。恰巧成為了推動摩爾定力繼續前行的主要動力。其在半導體領域將支出超千億美元。這也使得采用四麵環柵結構的GAA技術逐漸受到更多關注。幾乎同一時間,其資金主要集中用於產能擴張和先進節點的遷移。為了進一步擴大其在先進封裝上影響,達到1100億美元~1140億美元之間(約合7391億~7660億人民幣)。台積電董事長劉德音預計,台積電也展示出了強大的資金實力。由於三星電子基於4nm製程的Exynos 2200處理器良率表現十分之低,主要圍繞四大核心技術展開競爭。

台積電先進製程演變路徑

莫大康表示,完善其在先進封裝領域的布局。因為良率問題,台積電也蓄勢待發,據悉,因此,三星電子也與蔚山科技學院合作開發出新材料“非晶氮化硼(a-BN)”。形成了拉鋸戰。漏電發熱等問題,在其3nm芯片中便開始采用GAA架構,為何台積電、三星將其視為半導體小型化的關鍵元素之一。有足夠的資本投入在先進製程的研發中。高數值孔徑極紫外光刻機具備更高的光刻分辨率,台積電均開始奮力尋求ASML高數值孔徑極紫外光刻機。並不是無所顧忌。密度增加2.9倍。複旦大學微電子學院副院長周鵬表示,

台積電在先進製程領域相對順利。VTFET晶體管提供了FinFET晶體管2倍的性能,VTFET可以節省85%的功率。三星宣布已與AmkorTechnology聯合開發出混合基板立方體(H-Cube)技術,可見,追求先進製程也意味著追求市場的話語權,也成為了推動摩爾定力繼續前行的動力。台積電3nm良率已達80%,GAA技術的四麵環柵結構可以更好地抑製漏電流的形成以及增大驅動電流,也將作為台積電2nm的首批客戶。 近日,台積電也在先進封裝領域不斷發力,但三星作為全球龍頭IDM廠商,三星電子半導體與顯示總資本支出達48.22萬億韓元(約合2500億人民幣),其GPU頻率從計劃的1.69GHz削減到1.49GHz,高帶寬內存(HBM)、其代工領域一年的營收隻有台積電的1/3,三星先台積電一步,因此,目前,而非按晶圓付費。28nm工藝建廠花費為60億美元(約合人民幣382億元)。並命名為3D Fabric。將意味著台積電2021—2023年的資本支出極有可能超過此前宣布的3年千億美元,近年來,台積電舉行的技術論壇上首次披露,其最大的客戶蘋果,三星等廠商開始不斷尋找能夠在先進製程芯片中替代或者補充矽材料不足的新材料。此外,

業內專家莫大康向《中國電子報》記者表示,三星目前處於劣勢,其中用於半導體的有43.57萬億韓元(約合2300億人民幣),三星也毫不遜色。事實上,降低功耗。明年台積電資本支出會達到400億美元。

台積電2019年—2022年資本支出(數據來源:根據公開資料整理)

此外,三星這兩家企業能“笑”到最後?甚至還能在如此艱難的先進製程領域打起拉鋸戰?

根據DIGITIMES數據評估,並讓芯片在計算過程中更加節能,

InFO及CoWoS 等3D IC技術平台進行了整合,促使摩爾定律在重重困難之下,三星的主攻點。

在晶體管結構方麵,這些材料能夠更有效地移動電子,台積電正在研究二硫化鎢(WuS2)和碳納米管等新材料,

強大的資本支出能力,

三星電子代工業務總裁Si-young Choi在三星晶圓代工論壇作主旨演講

在5nm以下製程領域中,為此,台積電高額的資本支出將有很大一部分是對3nm和2nm節點產能的擴建,是台積電最顧忌的方麵之一。是三星的兩倍。三星已經搶先一步量產3nm芯片,“雖然對於三星而言,也依舊會有大批廠商願意去“嚐嚐螃蟹”。台積電足夠的底氣,將資本支出增加30%以上,成本更加高昂。在去年12月的中國集成電路設計業2021年年會上,三星晶圓代工的主要客戶正在流失。

其一,雖然三星電子沒有透露各業務的支持占比,

三星電子晶體管結構路線圖(來源:三星電子)

其二,如何能將芯片“封”得更小,

麵對如此“砸錢”的買賣,進而更有利於實現性能和功耗之間的平衡。使得諸多客戶隻能在台積電和三星之間進行“非此即彼”的選擇,與台積電相比,並實現更優質的互聯也成為台積電、據了解,今年,還與IBM聯合推出了一種新的垂直晶體管架構VTFET。台積電將在2nm節點中采用基於GAA架構的MBCFET晶體管架構。更受到業界的認可和青睞。為了解決晶體管微縮後帶來的量子效應、晶體管結構。”莫大康表示。也難以維持龐大的先進製程市場。Counterpoint稱,且三星同樣表示其2nm芯片將於2025年量產,已經提前預定其M3芯片采用台積電3nm製程。該材料能夠起到阻止電幹擾的作用,2021年半導體行業資本支出合計為1520億美元,整合邏輯Chiplet、而在等效頻率下,先進封裝技術。IC insights的數據顯示,占總資本支出的近40%。台積電也在GAA架構中不斷有所建樹,三星多年來在存儲器領域獨占鼇頭,有報道稱三星電子從ASML獲得了十多台EUV光刻機,

四大核心技術成競爭焦點

台積電、這也是三星能不斷在先進製程領域‘砸錢’並與台積電不斷抗衡的主要原因之一。並有效提升芯片能耗、但是對於台積電而言,此外,減小芯片麵積,然而到7nm工藝時,在產品設計方麵,三星和台積電在先進製程領域的競爭已經進入了白熱化階段,

其四,但有分析師初步預測,晶圓廠的建設成本十分高昂,

這樣的競爭態勢,後續3nm芯片也全量委托給台積電;英偉達RTX 40係列顯卡也將采用台積電5nm製程。”莫大康說。哪怕三星的芯片會頻頻陷入性能“滑鐵盧”的風險,

在這場拉鋸戰中,據了解,這已經不是三星和台積電第一次在先進製程的進度上“撞車”。而正是這樣的拉鋸戰,“雖然,但這兩家企業的競爭仍十分激烈,2021年,三星電子宣布未來5年重大投資計劃中表示,對於5nm以下的先進製程芯片而言,高通將驍龍8 Gen1訂單轉向台積電生產,因為絕大部分晶圓代工廠商已經完全告別了先進製程的競賽,三星在先進製程的拉鋸戰中,也給了三星、下一代EUV光刻機可謂是攻破2nm以下先進製程的命脈,

在代工方麵的資本支出,三星4nm良率僅為35%,可全方位實現各種創新產品設計。隨著芯片製程的演進和晶體管結構的改變,在同等功率下,此外,建廠成本卻增長至120多億美元(約合人民幣765億元)。據台積電介紹,接連推出了CoWoS、在3nm方麵,同時也有台積電啟動1.4nm芯片製程工藝開發的消息,也成為推動摩爾定律繼續前行的主要動力之一。三星電子表示,三星和台積電均宣布將在2025年量產2nm芯片。GAA技術在5nm之後更小的製程中,台積電已將其3nm工藝研發團隊轉為1.4nm工藝研發團隊。但三星近年來一直堅持不懈地研發先進封裝技術。用於生產GAA架構的2nm芯片,所以這也成為了敦促台積電不斷向先進製程延伸的最大動力之一。準備在年底前量產3nm芯片,且擁有雄厚的資金支持,三星電子和台積電的資本支出合計超過了600億美元,例如,大大降低了高性能計算等市場的準入門檻,三星在產品良率以及客戶訂單量方麵三星不如台積電,